Transaction Level Model Generation

HDL Verifier™ integrates with Simulink® Coder™ or Embedded Coder® to export SystemC™ TLM-compatible transaction-level models. You can integrate this component into your HDL simulation as a behavioral model.

The TLM generation tool provides a default socket and memory configuration. To customize the socket and memory map of the TLM component, provide an IP-XACT™ file. You can configure the generated component to use a SystemC thread or a callback function.

HDL Verifier generates a TLM test bench, test vectors, and a makefile to verify the component and assist with integration into your HDL simulator environment.

To use this functionality, download and install the ASIC Testbench for HDL Verifier add-on.

Topics

Generate TLM Component and Test Bench

- Get Started with TLM Generator

This example shows how to configure a Simulink® model to generate a SystemC™/TLM component using the tlmgenerator target for either Simulink Coder™ or Embedded Coder®. - The TLM Generation Process

After you obtain the TLM component files generated by HDL Verifier software, you can compile the TLM component and the optional test bench with OSCI SystemC libraries and the OSCI TLM libraries. - TLM Generation Algorithms

The algorithm you use to generate the TLM component can be made of any combination of Simulink blocks that can generate C code. - Subsystem Guidelines and Limitations

Most subsystems that can be converted to C code are suitable for generating a TLM component. - TLM Component Architecture

The TLM generator exports a target TLM component from a Simulink model subsystem. - Generated TLM Files

HDL Verifier software generates the following files: - TLM Component Generation Workflow

The following workflow lists the steps required to generate a TLM component using HDL Verifier software:

Define Memory Map

- Prepare IP-XACT File for Import

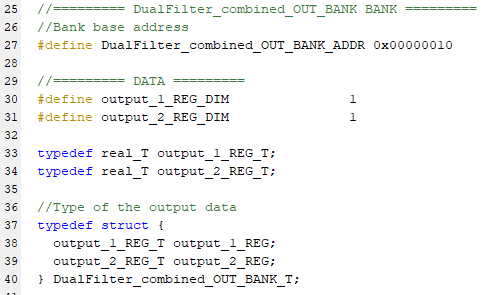

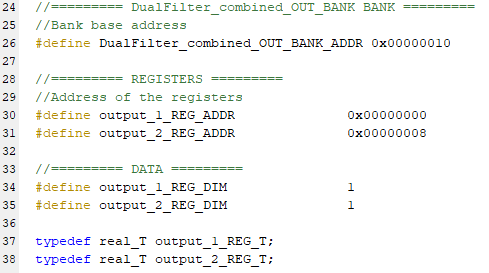

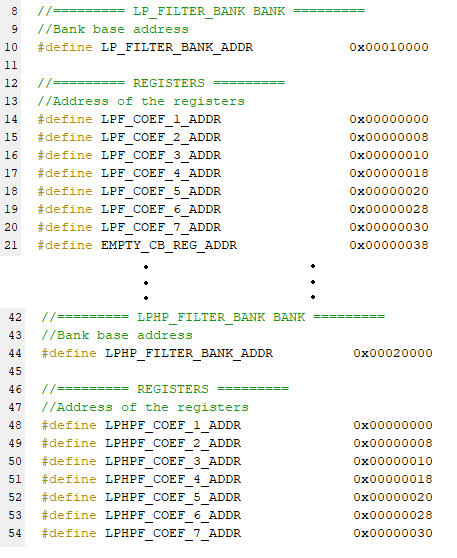

To customize the TLM interface of the component you want to generate, you can import your own IP-XACT XML file into the TLM generator. - Contents of Generated IP-XACT File

The TLM generator automatically generates an IP-XACT file that complies with IEEE® Standard for IP-XACT 1685-2009. - Implement Memory Map with SCML

The SystemC Modeling Library (SCML) is a TLM 2.0 compatible API library for creating TLM model interfaces for use with Synopsys® prototyping tools.

Export TLM Component

- Export TLM Component

After code generation completes, go to your working folder. - TLM Component Constructor

Describes the generated TLM components constructor and default parameters, with information for changing those parameters. - Testing TLM Components

The test bench generation option is controlled by the TLM Testbench tab of the Configuration Parameters dialog box.