Integration with Third-Party EDA Tools

Generate a Default Script

The coder generates scripts as part of the code and test bench generation process. Script files are generated in the target folder.

When HDL code is generated for a filter, filt, the

coder writes these script files.

filt_compile.do: Mentor Graphics® ModelSim® compilation script. This script contains commands to compile the generated filter code, but not to simulate it.

When test bench code is generated for a filter filt,

the coder writes these script files.

filt_tb_compile.do: Mentor Graphics ModelSim compilation script. This script contains commands to compile the generated filter and test bench code.filt_tb_sim.do: Mentor Graphics ModelSim simulation script. This script contains commands to run a simulation of the generated filter and test bench code.

You can enable or disable script generation and customize the names and content of generated script files by:

Passing properties as

'Name',Valuearguments to thegeneratehdlfunction. See HDL Synthesis and Workflow Automation Properties.Setting the corresponding options in the Generate HDL tool. Select the EDA Tool Scripts tab, and click Compilation script or Simulation script from the menu in the left column. See Customize Scripts for Compilation and Simulation.

Structure of Generated Script Files

A generated EDA script consists of three sections, which are generated and executed in this order.

An initialization (

Init) phase. TheInitphase performs required setup actions, such as creating a design library or a project file.A command-per-file phase (

Cmd). This phase of the script is called iteratively, once per generated HDL file.A termination phase (

Term). This phase is the final execution phase of the script. One application of this phase is to execute a simulation of HDL code that was compiled in theCmdphase.

The coder generates scripts by passing format character vectors to the

fprintf function. Using the UI options (or

generatehdl properties) summarized in these sections,

you can pass in customized format character vectors to the script generator.

Some of these format character vectors take arguments, such as the top-level

entity or module name.

You can use valid fprintf formatting characters. For

example, '\n' inserts a newline into the script file.

Customize Scripts for Compilation and Simulation

To view and set options for generated scripts:

Open the Generate HDL tool.

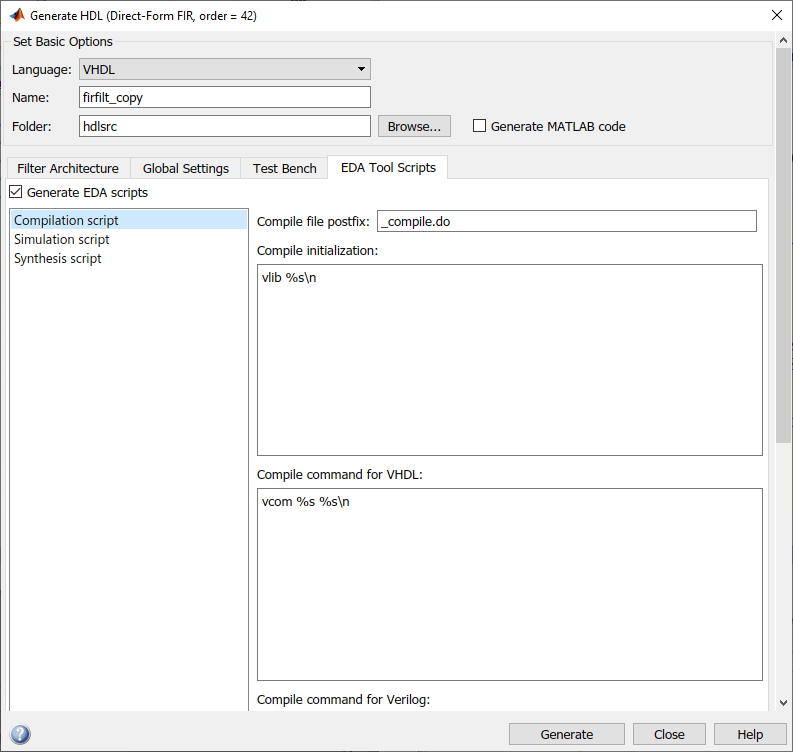

Click the EDA Tool Scripts tab.

The Compilation script options group is selected, as shown.

The Generate EDA scripts option controls the generation of script files. By default, this option is selected, as shown in the preceding image.

If you want to disable script generation, clear this check box.

The list on the left of the tool lets you select from several categories. Select a category and set the options as desired. The categories are:

Compilation script: customize scripts for compilation of generated VHDL® or Verilog code. See Compilation Script Options.

Simulation script: customize scripts for HDL simulators. See Simulation Script Options.

Synthesis script: customizing scripts for synthesis tools. See Automation Scripts for Third-Party Synthesis Tools.

The custom character vectors for each section are passed to

fprintfto write each section of the selected script. You can use format character vectors supported by thefprintffunction. Some of the character vectors include implicit arguments.Option Implicit arguments Compile initialization Library name Compile command for VHDL and Compile command for Verilog Contents of the Simulator flags option (an empty character vector,

'', by default)File name of the current module

Compile termination No implicit argument Compile initialization No implicit argument Simulation command Library name

Top-level module or entity name

Simulation termination No implicit argument

Compilation Script Options

The figure shows the Compilation script pane, with the options set to their default values.

The coder generates a script called

firfilt_copy_compile.do:

vlib work vcom firfilt_copy.vhd

firfilt_copy_tb_compile.dovlib work vcom firfilt_copy.vhd vcom firfilt_copy_tb.vhd

Setting Simulator Flags for Compilation Scripts. You have the option of inserting simulator flags into your generated compilation scripts. This option is included in the compilation scripts for both the standalone filter and the test bench. For example, you can specify a compiler version. To specify the flags:

Click Test Bench in the Generate HDL tool.

Type the flags of interest in the Simulator flags field. In the figure, the tool specifies that the Mentor Graphics ModelSim simulator use the

-93compiler option for compilation.

Command-Line Alternative: Specify

simulator flags with the SimulatorFlags property of the generatehdl

function.

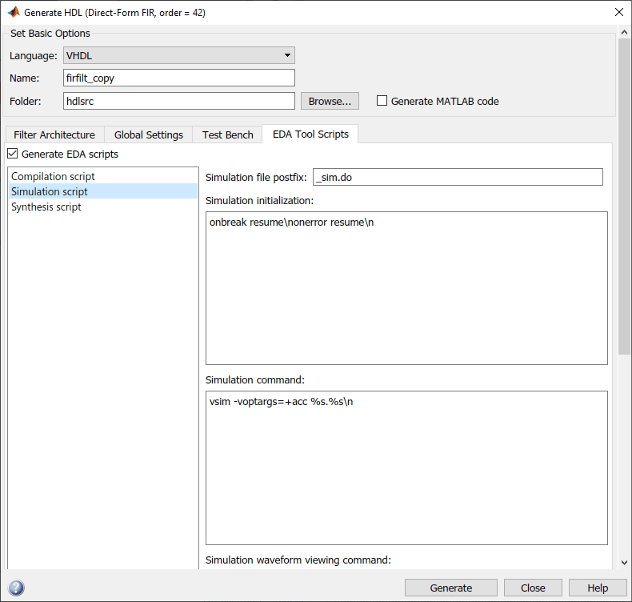

Simulation Script Options

The coder generates a simulation script when you generate a test bench. The figure shows the Simulation script pane, with the options set to their default values.

The coder generates a script called firfilt_copy_tb_sim.do:

onbreak resume onerror resume vsim -voptargs=+acc work.firfilt_copy_tb add wave sim:/firfilt_copy_tb/u_firfilt_copy/clk add wave sim:/firfilt_copy_tb/u_firfilt_copy/clk_enable add wave sim:/firfilt_copy_tb/u_firfilt_copy/reset add wave sim:/firfilt_copy_tb/u_firfilt_copy/filter_in add wave sim:/firfilt_copy_tb/u_firfilt_copy/filter_out add wave sim:/firfilt_copy_tb/filter_out_ref run -all

Synthesis Script Options

For information about synthesis script options, see Automation Scripts for Third-Party Synthesis Tools.