FPGA-in-the-Loop Simulation

What is FPGA-in-the-Loop Simulation?

Overview

FPGA-in-the-loop (FIL) simulation provides the capability to use Simulink® or MATLAB® software for testing designs in real hardware for any existing HDL code. The HDL code can be either manually written or software generated from a model subsystem.

You must have HDL code to perform FIL simulation. There are two FIL workflows:

You have existing HDL code (FIL wizard).

Note

The FIL wizard uses any synthesizable HDL code including code automatically generated from Simulink models by HDL Coder™ software

You have MATLAB code or a Simulink model and an HDL Coder license (HDL workflow advisor).

Note

When you use FIL in the Workflow Advisor, HDL Coder uses the loaded design to create the HDL code.

No matter which workflow you choose, FIL performs the following processes when it creates the block or System object™:

Generates a FIL block or FIL System object that represents the HDL code

Provides synthesis, logical mapping, place-and-route (PAR), programming file generation, and communications channel.

Loads the design onto an FPGA

All these capabilities are designed for a particular board and tailored to your RTL code.

As part of FIL simulation, the block or System object and your model or application:

Transmits data from Simulink or MATLAB to the FPGA

Receives data from the FPGA

Exercises the design in a real environment

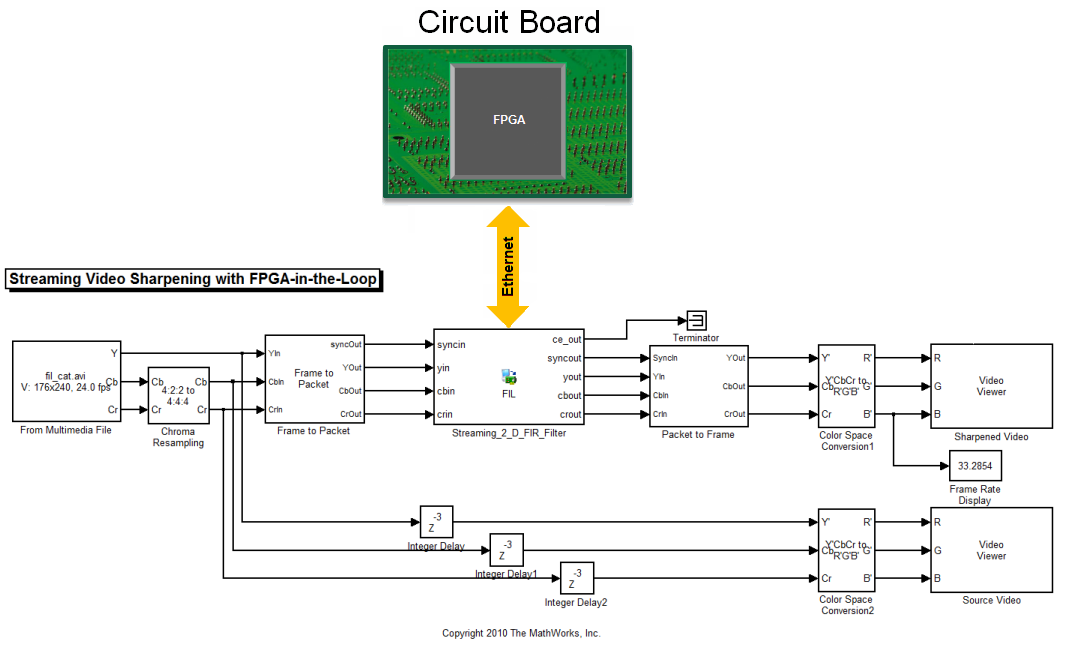

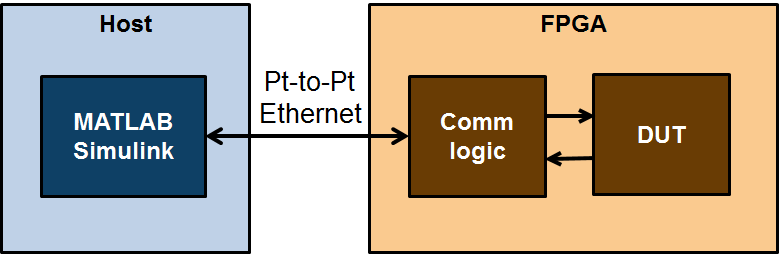

FIL Communications. The following figure demonstrates how HDL Verifier™ communicates between Simulink and the FPGA board using FIL simulation.

Note

HDL Verifier assumes that there is only one download cable connected to the host computer, and that the FPGA programming software can automatically detect this connection. If not, use FPGA programming software to program your FPGA with the correct options.

System-Level View. All DUT I/Os are routed to Simulink through the FIL communication logic.

Communication Channel

FIL provides the communication channel for sending and receiving data between Simulink and the FPGA. This channel can be a JTAG, Ethernet, PCI Express®, or USB Ethernet connection. Communication between Simulink and the FPGA is strictly synchronized to provide a reliable verification environment.

Downstream Workflow Automation

To create the FIL programming file, the software performs the following tasks:

Generates HDL code for the specified DUT and creates an ISE project.

Along with your FPGA design software, synthesizes, maps, places and routes, and creates a programming file for the FPGA.

Downloads the programming file to the FPGA on the development board through the normal configuration connection. Typically, that connection is a serial line over a USB cable (see the board user guide for how to make this connection).

For FIL simulation blocks, clicking Load on the FIL block mask initiates the programming file download.

For FIL simulation System objects, issuing the

programFPGAmethod initiates the programming file download.

What You Need To Know

For FIL simulation, you must have the following items or information ready:

For FIL wizard:

Provide HDL code (either manually written or software generated) for the design you intend to test.

Select HDL files and specify the top-level module name.

Review port settings and make sure the FIL wizard identified input and output signals and signal sizes as expected.

If you are using Simulink, provide a Simulink model ready to receive the generated FIL block.

For HDL Workflow Advisor:

You can generate code and run FIL from any suitable Simulink model. Follow the workflow for

FPGA-in-the-Loop. See FIL Simulation with HDL Workflow Advisor for Simulink. For MATLAB code, see the workflow described in FIL Simulation with HDL Workflow Advisor for MATLAB.