What Is FPGA Image Processing?

FPGA image processing performs compute-intensive video and image processing using dedicated hardware that delivers low latency and high throughput computation. These techniques often involve pre-processing an incoming video stream for further processing in software or a deep learning network.

You can use MATLAB® and Simulink® together to explore implementation options for your FPGA image processing algorithms. Options include partitioning between hardware and software, adding hardware micro-architecture, and fixed-point quantization. At each step, you can simulate the new version and compare the results to the reference algorithm.

Get started quickly with hardware-proven FPGA image processing blocks, example designs, and utilities from Vision HDL Toolbox™. You can use these blocks to design, explore, and simulate your FPGA image processing algorithms without having to write HDL code.

Hardware-proven FPGA image processing blocks available include:

- Edge and corner detection

- Bilateral and median filtering

- Conversions such as color space, chroma resampling, gamma correction, and bird’s-eye view

- Morphological closing, opening, dilation, and erosion

- Utilities such as line buffer, pixel stream aligner, and ROI selector

Figure 1. Using hardware-proven and configurable FPGA image processing blocks for pre-processing a video stream.

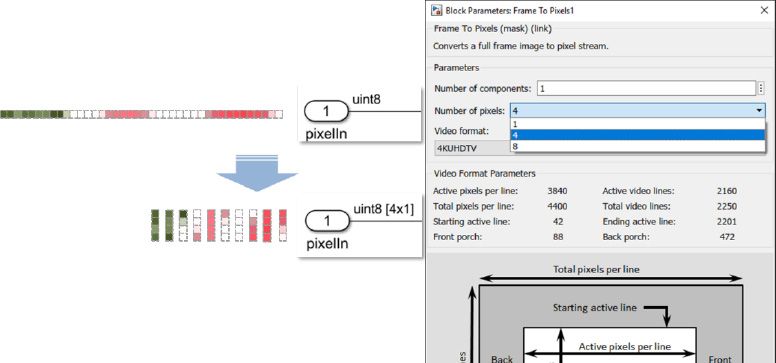

Because FPGA image processing operates on a stream of pixels, many of these blocks inherently support processing of multiple pixels or multiple components in parallel. This allows you to rapidly explore the benefits and costs of different levels of parallelism.

Figure 2. Explore tradeoffs associated with different levels of parallelism for pixel and component processing.

After you have run sufficient simulations to verify that your FPGA image processing algorithm meets the required functionality and performance, you can use HDL Coder™ to generate synthesizable VHDL or Verilog for deployment.

Examples and How To

Videos

Software Reference

- Frame To Pixels and Pixels To Frame conversion - Documentation

- Hardware-ready image and video processing algorithms - Documentation

- Prototype Vision Algorithms on Zynq-Based Hardware - Documentation

See also: HDL Coder™, HDL Verifier™