Generate Simulink Real-Time Interface Subsystem for Simscape Two-Level Converter Model

This example shows how to generate a Simulink® Real-Time Interface subsystem for a Simscape™ two-level converter plant model. You can then deploy the interface model on the Speedgoat® FPGA I/O module. This example uses the Speedgoat IO334-325k module.

Real-Time Simulation

Simulating the plant model on the FPGA provides:

Real-time Simulation: Hardware-in-the-loop provides real-time simulation of your Simscape plant model on the target hardware.

Hardware Acceleration: Accelerated simulation of complex physical systems on hardware while reconfigurable FPGAs provide rapid prototyping.

To use the workflow:

Develop the Simscape model and convert it into an implementation model by using the Simscape HDL Workflow Advisor.

Generate HDL code and deploy the code to the Speedgoat I/O module by using the HDL Workflow Advisor.

Setup and Configuration

Before deploying your algorithm on the Speedgoat I/O module:

1. Install the latest version of Xilinx® Vivado® as listed in HDL Language Support and Supported Third-Party Tools and Hardware.

Then, set the tool path to the installed Xilinx Vivado executable by using the hdlsetuptoolpath function.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2019.2\bin\vivado.bat')

2. For real-time simulation, set up the development environment and target computer settings. See Get Started with Simulink Real-Time (Simulink Real-Time).

3. Install the Speedgoat I/O Blockset and the Speedgoat HDL Coder Integration packages. See Install Speedgoat HDL Coder Integration Packages.

Two-Level Converter Ideal Model

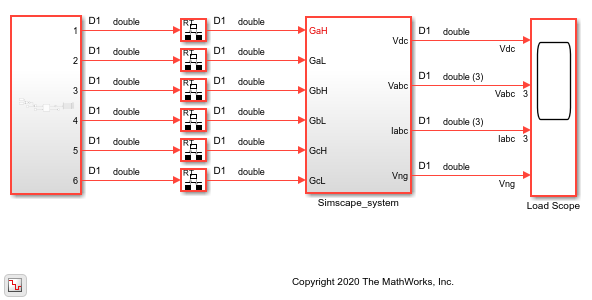

To open this model, at the MATLAB® command prompt, enter:

open_system('TwoLevelConverter_HDL') set_param('TwoLevelConverter_HDL','SimulationCommand','update')

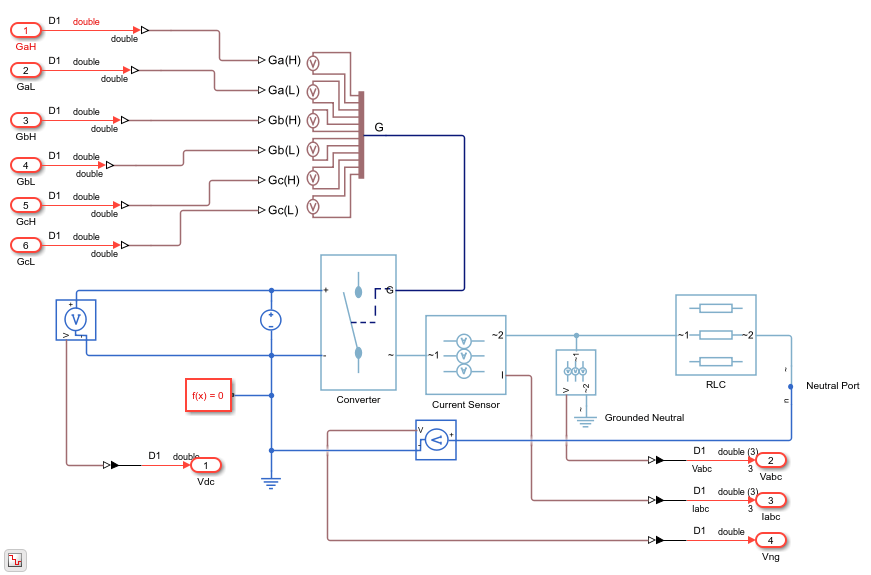

open_system('TwoLevelConverter_HDL/Simscape_system')

The Simscape subsystem receives six-switch controlling pulses as input. The Simscape subsystem acts as a generator that uses a two-level, carrier-based PWM method to:

Sample a reference wave.

Compare the sample to a triangular carrier wave.

Generate a switch-on pulse if a sample is higher than the carrier signal or a switch-off pulse if a sample is lower than the carrier wave.

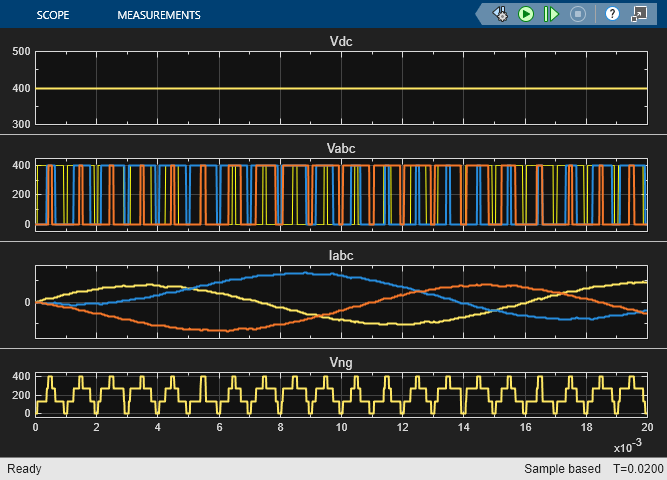

Simulate the model.

sim('TwoLevelConverter_HDL') open_system('TwoLevelConverter_HDL/Load Scope')

Generate HDL Implementation Model

To generate an implementation model, use the Simscape HDL Workflow Advisor. Run the sschdladvisor function for your model:

sschdladvisor('TwoLevelConverter_HDL')

To generate the implementation model, in the Simscape HDL Workflow Advisor, keep the default settings for the tasks, and then run the tasks. You see a link to the model in the Generate implementation model task. This model has the same name as the original model prefixed with gmStateSpaceHDL.

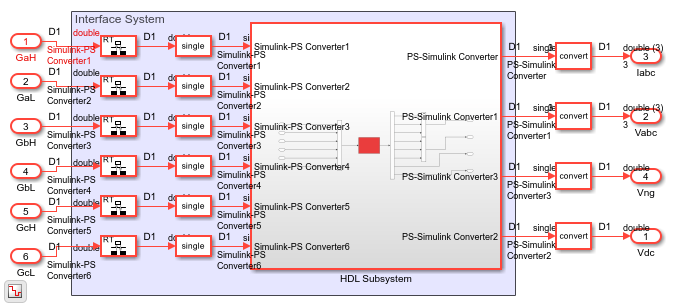

To open the implementation model, enter:

load_system('gmStateSpaceHDL_TwoLevelConverter_HDL') open_system('gmStateSpaceHDL_TwoLevelConverter_HDL/Simscape_system') set_param('gmStateSpaceHDL_TwoLevelConverter_HDL','SimulationCommand','update')

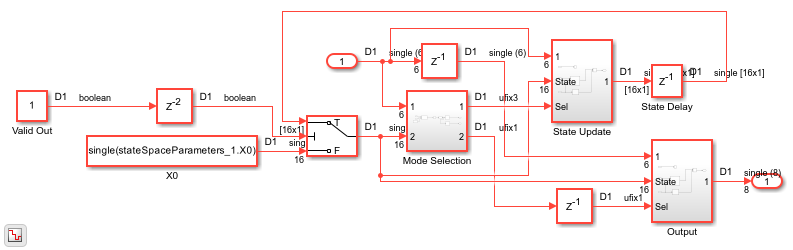

The implementation model replaces the Simscape subsystem with the HDL algorithm that performs the state-space computations. When you navigate inside this subsystem, you see several delays, adders, and Matrix Multiply blocks that model the state-space equations. From and Goto blocks inside this subsystem provide the same input as that of the original model to the HDL Subsystem.

open_system('gmStateSpaceHDL_TwoLevelConverter_HDL/Simscape_system/HDL Subsystem/HDL Algorithm')

HDL Workflow Advisor

The HDL Workflow Advisor guides you through HDL code generation and the FPGA design process. Use the Advisor to:

Check the model for HDL code generation compatibility and fix incompatible settings.

Generate HDL code, test bench, and scripts to build and run the code and test bench.

Perform synthesis and timing analysis.

Deploy the generated code on SoCs, FPGAs, and Speedgoat I/O modules.

To open the HDL Workflow Advisor for a subsystem inside the model, use the hdladvisor function.

load_system('sschdlexTwoLevelConverterIgbtExample') hdladvisor('sschdlexTwoLevelConverterIgbtExample/Simscape_system')

The left pane contains folders that represent a group of related tasks. Expanding the folders and selecting a task displays information about that task in the right pane. The right pane contains simple controls for running the task to advanced parameters and option settings that control code and test bench generation. To learn more about each task, right-click that task, and select What's This?. See Getting Started with the HDL Workflow Advisor.

Deploy Two Level Ideal Converter Model to Speedgoat IO334-325K Module

1. Open the HDL Workflow Advisor for the implementation model.

hdladvisor('gmStateSpaceHDL_TwoLevelConverter_HDL/Simscape_system/HDL Subsystem')

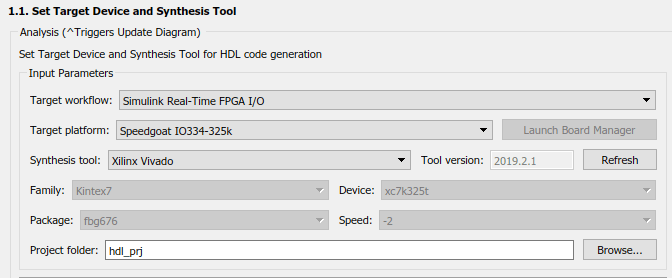

2. In Set Target Device and Synthesis Tool task, specify Target workflow as Simulink Real-Time FPGA I/O and Target platform as Speedgoat IO334-325K

3. Run the Set Target Reference Design task, select a value of x4 for the parameter PCIe lanes, and select Run This Task.

4. In Set Target Interface task, map the input and output single data type ports to PCIe Interface and select Run This Task.

5. Right-click Generate RTL Code and IP Core task and select Run to Selected Task. As the model uses vector data types, the Generate RTL Code and IP Core fails because the ScalarizePorts property must be set to dutlevel. Click the link to change this setting and rerun the task.

6. Run the workflow to the Generate Simulink Real-Time interface task. In Create Project task, you can open the Vivado project and see the implemented design. After the Generate Simulink Real-Time interface task passes, click the link to open the Simulink Real-Time Interface Model.

Export HDL Workflow to Script

For rapid prototyping, you can export the HDL Workflow Advisor settings to a script. The script is a MATLAB® file that you can run from the command line. You can then modify and run the script, or import the settings into the HDL Workflow Advisor User Interface.

To export an HDL Workflow script, after you run the tasks in the Advisor, select File > Export to Script. For this example, when you export to script, this file shows the settings you saved.

edit('hdlworkflow_slrt.m')

To import an HDL Workflow script, in the HDL Workflow Advisor, select File > Import from Script. Select the script file and click Open. The HDL Workflow Advisor updates the tasks with the imported script settings.

For an example that shows how to run the real-time application by deploying the FPGA bitstream, see Hardware-in-the-Loop Implementation of Simscape Model on Speedgoat FPGA I/O Modules.