Basic FIR Filter

Note

The Filter Design HDL Coder™ product will be discontinued in a future release. Instead, you can model hardware behavior, and generate HDL code by using System objects or Simulink® blocks from DSP HDL Toolbox™. These objects and blocks include hardware-friendly control signals and architecture options. To generate HDL code from DSP HDL Toolbox objects and blocks, you must also have the HDL Coder™ product.

For examples of modeling an FIR filter for hardware, see Fully Parallel Systolic FIR Filter Implementation (DSP HDL Toolbox) and Partly Serial Systolic FIR Filter Implementation (DSP HDL Toolbox). These examples use the Discrete FIR Filter (DSP HDL Toolbox) block. Equivalent

functionality is also available in the dsphdl.FIRFilter (DSP HDL Toolbox)

System object™.

Create a Folder for Your Tutorial Files

Set up a writable working folder outside your MATLAB® installation

folder to store files that will be generated as you complete your

tutorial work. The tutorial instructions assume that you create the

folder hdlfilter_tutorials on drive C.

Design a FIR Filter in Filter Designer

This section assumes that you are familiar with the MATLAB user interface and the Filter Designer. These instructions guide you through designing and creating a basic FIR filter using Filter Designer.

Start the MATLAB software.

Set your current folder to the folder you created in Create a Folder for Your Tutorial Files.

Start Filter Designer by entering the

filterDesignercommand in the MATLAB Command Window. The Filter Design & Analysis Tool appears.

In the Filter Design & Analysis Tool, check that these filter options are set.

Option Value Response Type LowpassDesign Method FIR EquirippleFilter Order Minimum order Options Density Factor: 20Frequency Specifications Units:

HzFs:

48000Fpass:

9600Fstop:

12000Magnitude Specifications Units:

dBApass:

1Astop:

80These settings are for the default filter design that the Filter Designer creates for you. If you do not have to change the filter, and Design Filter is grayed out, you are done and can skip to Quantize the Filter.

If you modified options listed in step 4, click Design Filter. The Filter Designer creates a filter for the specified design and displays this message in the Filter Designer status bar when the task is complete.

Designing Filter... Done

For more information on designing filters with the Filter Designer, see the DSP System Toolbox™ documentation.

Quantize the Filter

You must quantize filters for HDL code generation. To quantize your filter,

Open the basic FIR filter design you created in Design a FIR Filter in Filter Designer.

Click the Set Quantization Parameters button

in the left-side toolbar. The Filter

Designer displays a Filter arithmetic menu in the

bottom half of the window.

in the left-side toolbar. The Filter

Designer displays a Filter arithmetic menu in the

bottom half of the window.

Select

Fixed-pointfrom the Filter arithmetic list. Then selectSpecify allfrom the Filter precision list. The Filter Designer displays the first of three tabbed panels of quantization parameters across the bottom half of the window.

Use the quantization options to test the effects of various settings on the performance and accuracy of the quantized filter.

Set the quantization parameters as follows:

Tab Parameter Setting Coefficients Numerator word length 16Best-precision fraction lengths SelectedUse unsigned representation ClearedScale the numerator coefficients to fully utilize the entire dynamic range ClearedInput/Output Input word length 16Input fraction length 15Output word length 16Filter Internals Rounding mode FloorOverflow mode SaturateAccum. word length 40Click Apply.

For more information on quantizing filters with the Filter Designer, see the DSP System Toolbox documentation.

Configure and Generate VHDL Code

After you quantize your filter, you are ready to configure coder options and generate VHDL® code for the filter. This section guides you through starting the Filter Design HDL Coder UI, setting options, and generating the VHDL code and test bench for the basic FIR filter you designed and quantized in Design a FIR Filter in Filter Designer and Quantize the Filter.

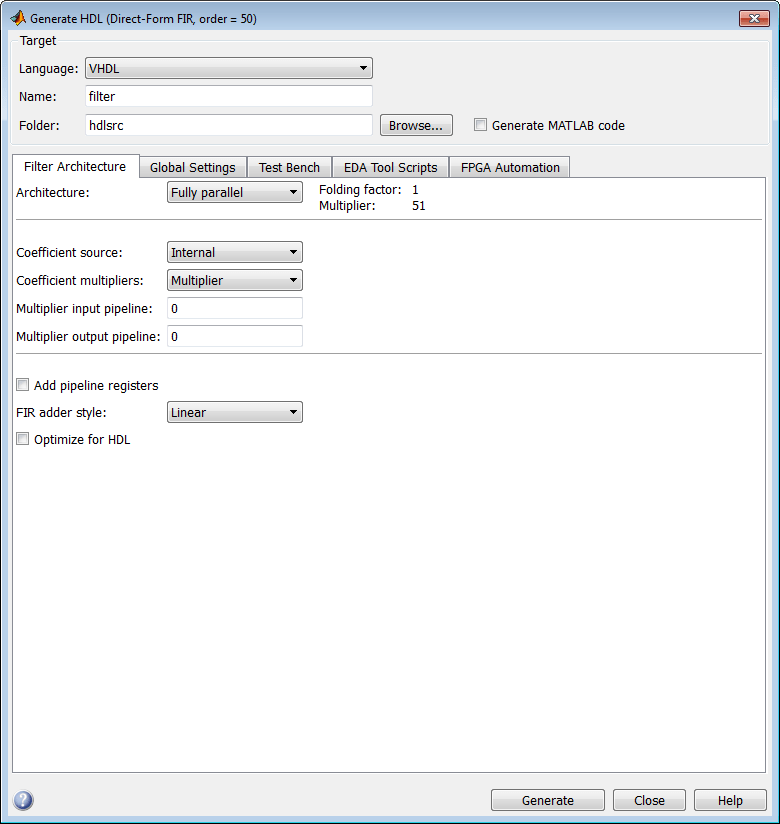

Start the Filter Design HDL Coder UI by selecting Targets > Generate HDL in the Filter Designer tool. The Filter Designer displays the Generate HDL tool.

Find the Filter Design HDL Coder online help.

In the MATLAB window, click the Help button in the toolbar or click Help > Product Help.

In the Contents pane of the Help browser, select the Filter Design HDL Coder entry.

Minimize the Help browser.

In the Generate HDL tool, click the Help button. A small context-sensitive help window opens. The window displays information about the tool.

Close the Help window.

Place your cursor over the Folder label or text box in the Target pane of the Generate HDL tool, and right-click. A What's This? button appears.

Click What's This? The context-sensitive help window displays information describing the Folder option. Configure the contents and style of the generated HDL code, using the context-sensitive help to get more information as you work. A help topic is available for each option.

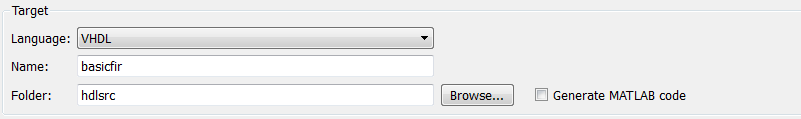

In the Name text box of the Target pane, replace the default name with

basicfir. This option names the VHDL entity and the file that contains the VHDL code for the filter.

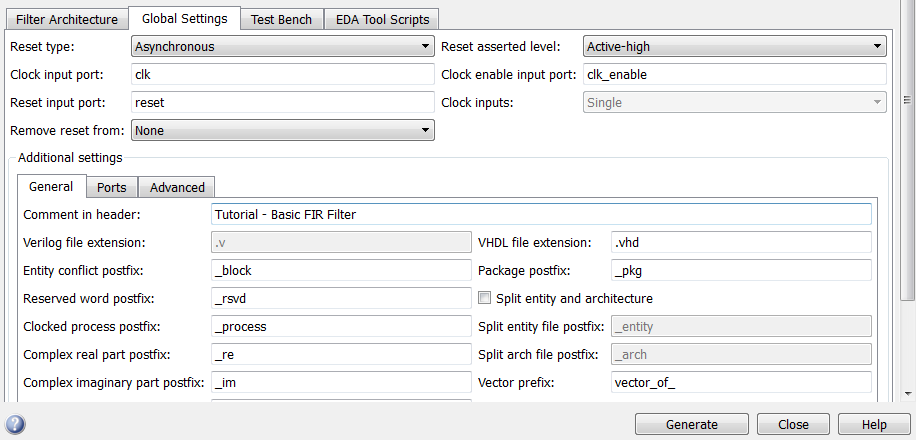

Select the Global settings tab of the UI. Then select the General tab of the Additional settings section of the UI. Type

Tutorial - Basic FIR Filterin the Comment in header text box. The coder adds the comment to the end of the header comment block in each generated file.

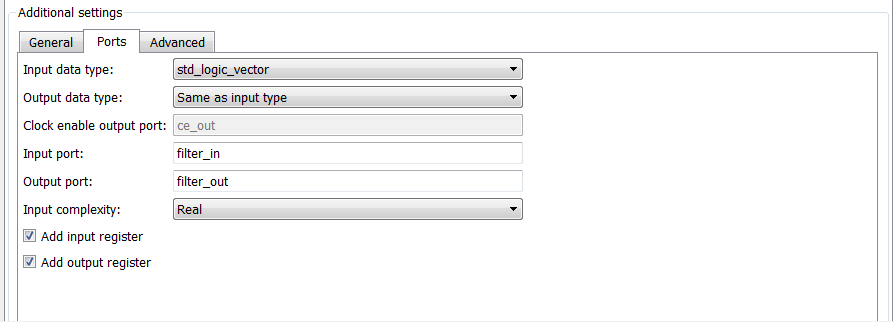

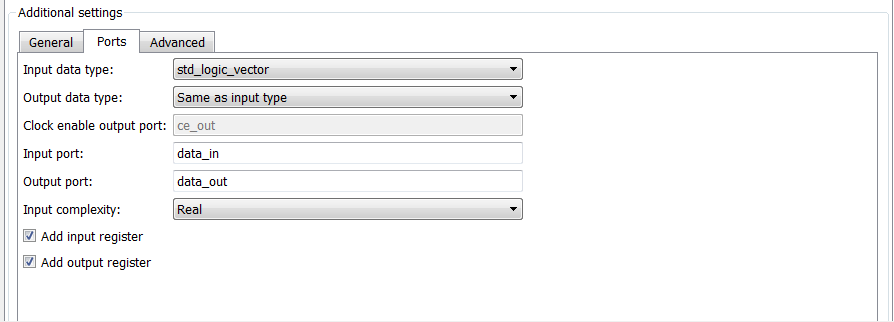

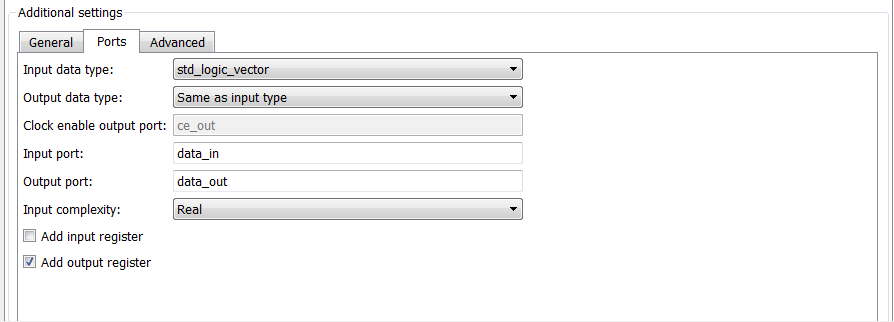

Select the Ports tab of the Additional settings section of the UI.

Change the names of the input and output ports. In the Input port text box, replace

filter_inwithdata_in. In the Output port text box, replacefilter_outwithdata_out.

Clear the check box for the Add input register option. The Ports pane now looks like this figure.

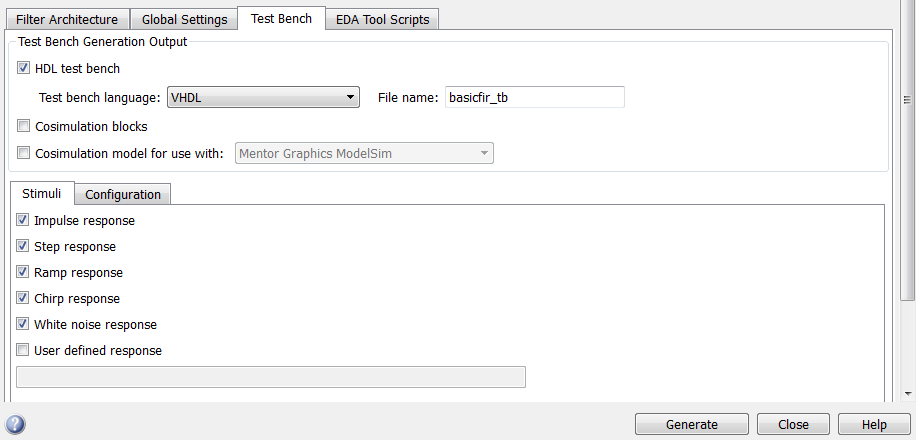

Click the Test Bench tab in the Generate HDL tool. In the File name text box, replace the default name with

basicfir_tb. This option names the generated test bench file.

Click Generate to start the code generation process.

The coder displays messages in the MATLAB Command Window as it generates the filter and test bench VHDL files:

### Starting VHDL code generation process for filter: basicfir ### Generating: C:\hdlfilter_tutorials\hdlsrc\basicfir.vhd ### Starting generation of basicfir VHDL entity ### Starting generation of basicfir VHDL architecture ### HDL latency is 2 samples ### Successful completion of VHDL code generation process for filter: basicfir ### Starting generation of VHDL Test Bench ### Generating input stimulus ### Done generating input stimulus; length 3429 samples. ### Generating Test bench: C:\hdlfilter_tutorials\hdlsrc\basicfir_tb.vhd ### Please wait ... ### Done generating VHDL Test Bench

As the messages indicate, the coder creates the folder

hdlsrcunder your current working folder and places the filesbasicfir.vhdandbasicfir_tb.vhdin that folder.Observe that the messages include hyperlinks to the generated code and test bench files. By clicking these hyperlinks, you can open the code files directly into the MATLAB Editor.

The generated VHDL code has these characteristics:

VHDL entity named

basicfir.Registers that use asynchronous resets when the reset signal is active high (1).

The table shows the names of the ports.

VHDL Port Name Input data_inOutput data_outClock input clkClock enable input clk_enableReset input resetAn extra register for handling filter output.

Clock input, clock enable input, and reset ports are of type

STD_LOGICand data input and output ports are of typeSTD_LOGIC_VECTOR.Coefficients are named

coeff, wherennis the coefficient number, starting with 1.Type-safe representation is used when zeros are concatenated:

'0' & '0'...Registers are generated with the statement

ELSIF clk'event AND clk='1' THENrather than with therising_edgefunction.The postfix

'_process'is appended to process names.

The generated test bench:

Is a portable VHDL file.

Forces clock, clock enable, and reset input signals.

Forces the clock enable input signal to active high.

Drives the clock input signal high (1) for 5 nanoseconds and low (0) for 5 nanoseconds.

Forces the reset signal for two cycles plus a hold time of 2 nanoseconds.

Applies a hold time of 2 nanoseconds to data input signals.

For a FIR filter, applies impulse, step, ramp, chirp, and white noise stimulus types.

When you have finished generating code, click Close to close the Generate HDL tool.

Explore the Generated VHDL Code

Get familiar with the generated VHDL code by opening and browsing through the file

basicfir.vhd in an ASCII or HDL simulator editor.

Open the generated VHDL filter file

basicfir.vhd.Search for

basicfir. This line identifies the VHDL module, using the value you specified for the Name option in the Target pane. See step 5 in Configure and Generate VHDL Code.Search for

Tutorial. This section is where the coder places the text you entered for the Comment in header option. See step 10 in Configure and Generate VHDL Code.Search for

HDL Code. This section lists coder options you modified in Configure and Generate VHDL Code.Search for

Filter Settings. This section describes the filter design and quantization settings as you specified in Design a FIR Filter in Filter Designer and Quantize the Filter.Search for

ENTITY. This line names the VHDL entity, using the value you specified for the Name option in the Target pane. See step 5 in Configure and Generate VHDL Code.Search for

PORT. ThisPORTdeclaration defines the clock, clock enable, reset, and data input and output ports. The ports for clock, clock enable, and reset signals are named with default character vectors. The ports for data input and output are named as you specified on the Input port and Output port options on the Ports tab of the Generate HDL tool. See step 12 in Configure and Generate VHDL Code.Search for

Constants. This section defines the coefficients. They are named using the default naming scheme,coeff, wherennis the coefficient number, starting with 1.Search for

Signals. This section of code defines the signals for the filter.Search for

process. ThePROCESSblock nameDelay_Pipeline_processincludes the defaultPROCESSblock postfix'_process'.Search for

IF reset. This code asserts the reset signal. The default, active high (1), was specified. Also note that thePROCESSblock applies the default asynchronous reset style when generating VHDL code for registers.Search for

ELSIF. This code checks for rising edges when the filter operates on registers. The defaultELSIF clk'eventstatement is used instead of the optionalrising_edgefunction.Search for

Output_Register. This section of code writes the filter data to an output register. Code for this register is generated by default. In step 13 in Configure and Generate VHDL Code, you cleared the Add input register option, but left the Add output register selected. Also note that thePROCESSblock nameOutput_Register_processincludes the defaultPROCESSblock postfix'_process'.Search for

data_out. This section of code drives the output data of the filter.

Verify the Generated VHDL Code

This section explains how to verify the generated VHDL code for the basic FIR filter with the generated VHDL test bench. This tutorial uses the Mentor Graphics® ModelSim® software as the tool for compiling and simulating the VHDL code. You can also use other VHDL simulation tool packages.

To verify the filter code, complete these steps:

Start your Mentor Graphics ModelSim simulator.

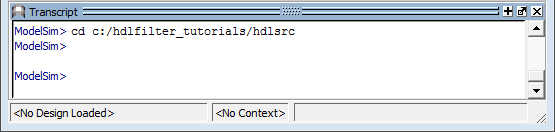

Set the current folder to the folder that contains your generated VHDL files. For example:

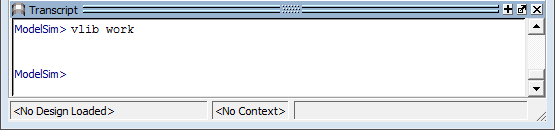

If desired, create a design library to store the compiled VHDL entities, packages, architectures, and configurations. In the Mentor Graphics ModelSim simulator, you can create a design library with the

vlibcommand.

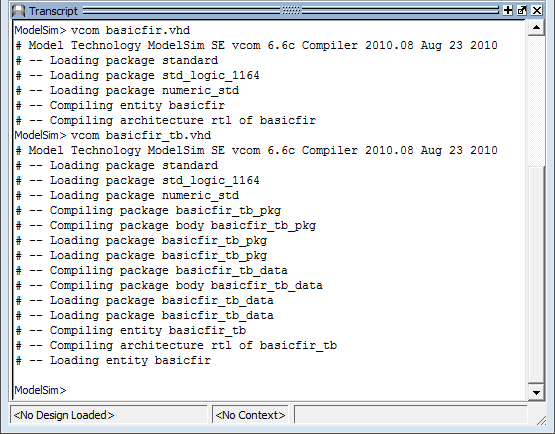

Compile the generated filter and test bench VHDL files. In the Mentor Graphics ModelSim simulator, you compile VHDL code with the

vcomcommand. These commands compile the filter and filter test bench VHDL code.vcom basicfir.vhd vcom basicfir_tb.vhd

This screen display shows the command sequence and informational messages displayed during compilation.

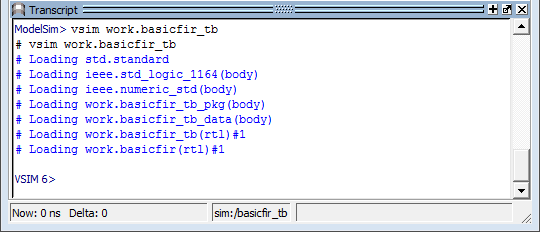

Load the test bench for simulation. The procedure for loading the test bench varies depending on the simulator you are using. In the Mentor Graphics ModelSim simulator, you load the test bench for simulation with the

vsimcommand. For example:vsim work.basicfir_tb

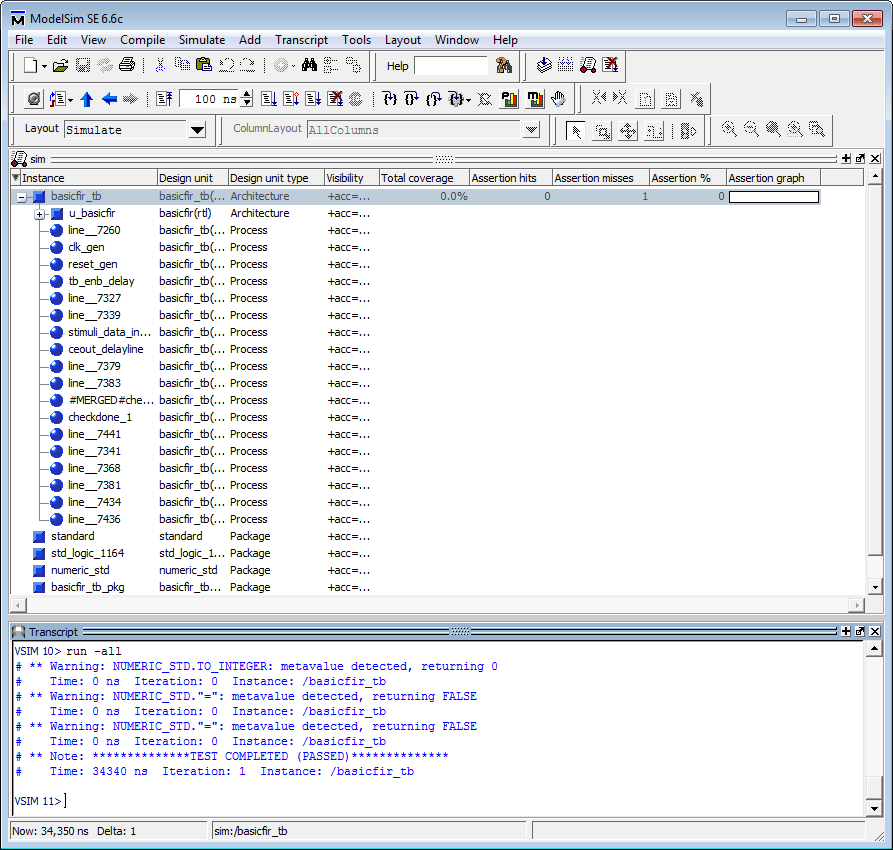

This figure shows the results of loading

work.basicfir_tbwith thevsimcommand.

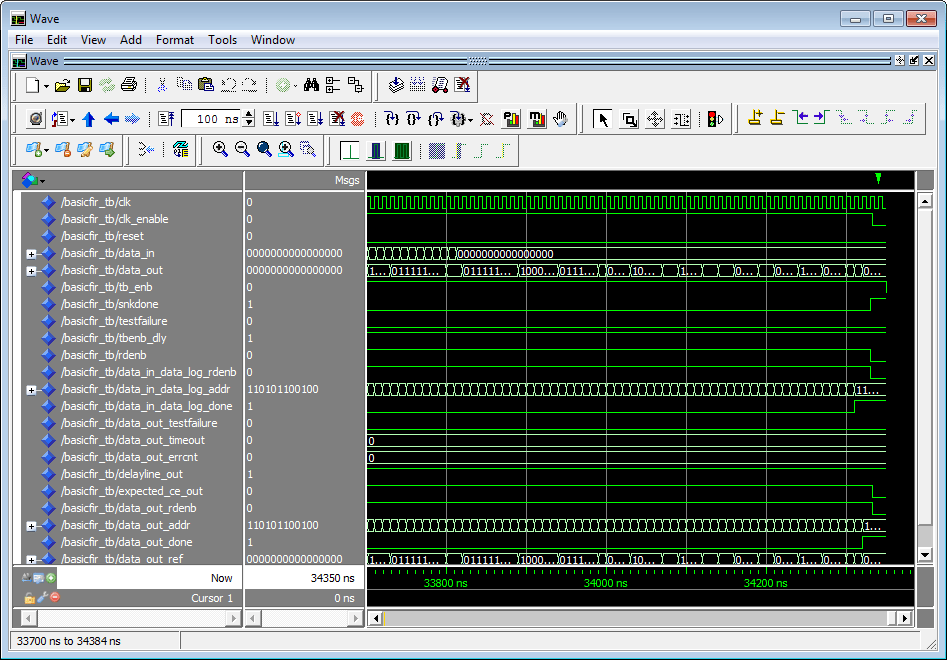

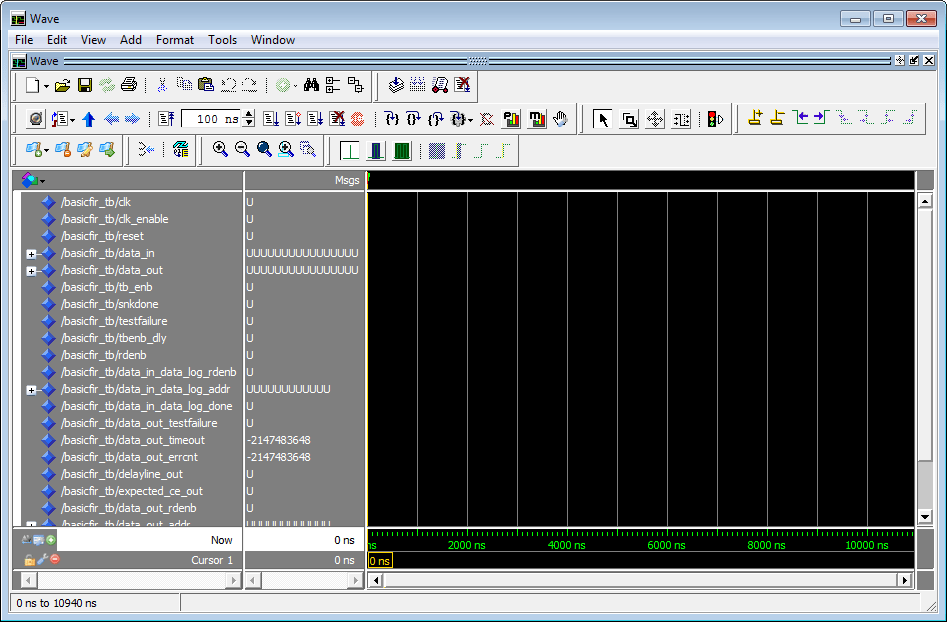

Open a display window for monitoring the simulation as the test bench runs. In the Mentor Graphics ModelSim simulator, use this command to open a wave window and view the results of the simulation as HDL waveforms.

This wave window opens.

To start running the simulation, issue the start simulation command for your simulator. For example, in the Mentor Graphics ModelSim simulator, you can start a simulation with the

runcommand.This figure shows starting a simulation with the

run -allcommand.

As your test bench simulation runs, watch for error messages. If error messages appear, interpret them as they pertain to your filter design and the HDL code generation options you selected. Determine whether the results are expected based on the customizations you specified when generating the filter VHDL code.

This wave window shows the simulation results as HDL waveforms.